About Me

Bridging Hardware Logic, Embedded Software & AI Systems

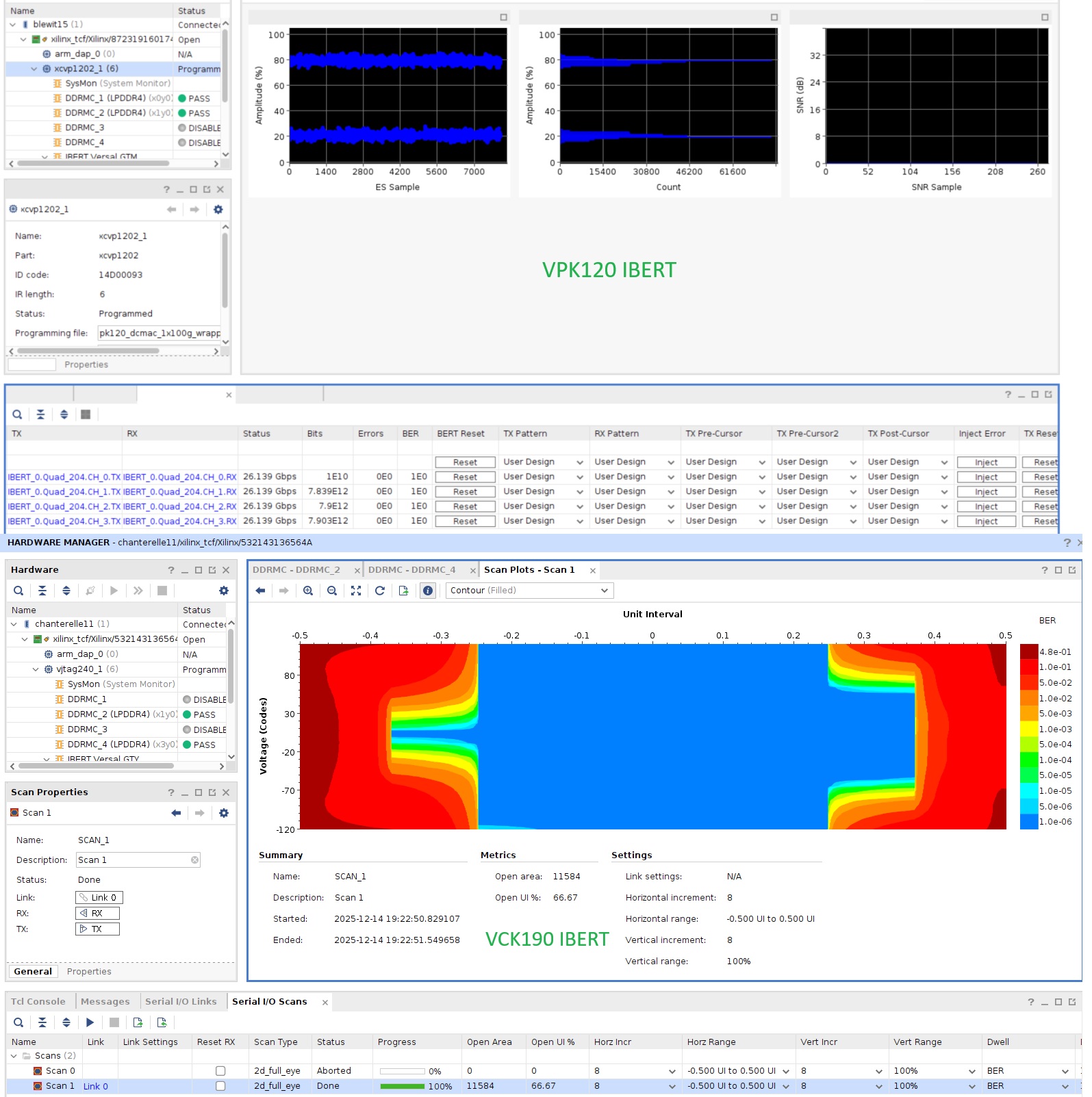

Sr. FPGA & Network System Engineer @ AMD

Specializing in High-Performance Computing (HPC) & Low-Latency Networking

I serve as the technical lead for AMD's Ethernet reference designs, ensuring data integrity across Versal ACAP and Zynq MPSoC platforms. My core expertise lies in bridging the gap between FPGA Logic (Verilog/RTL) and Embedded Software (Linux/Drivers).

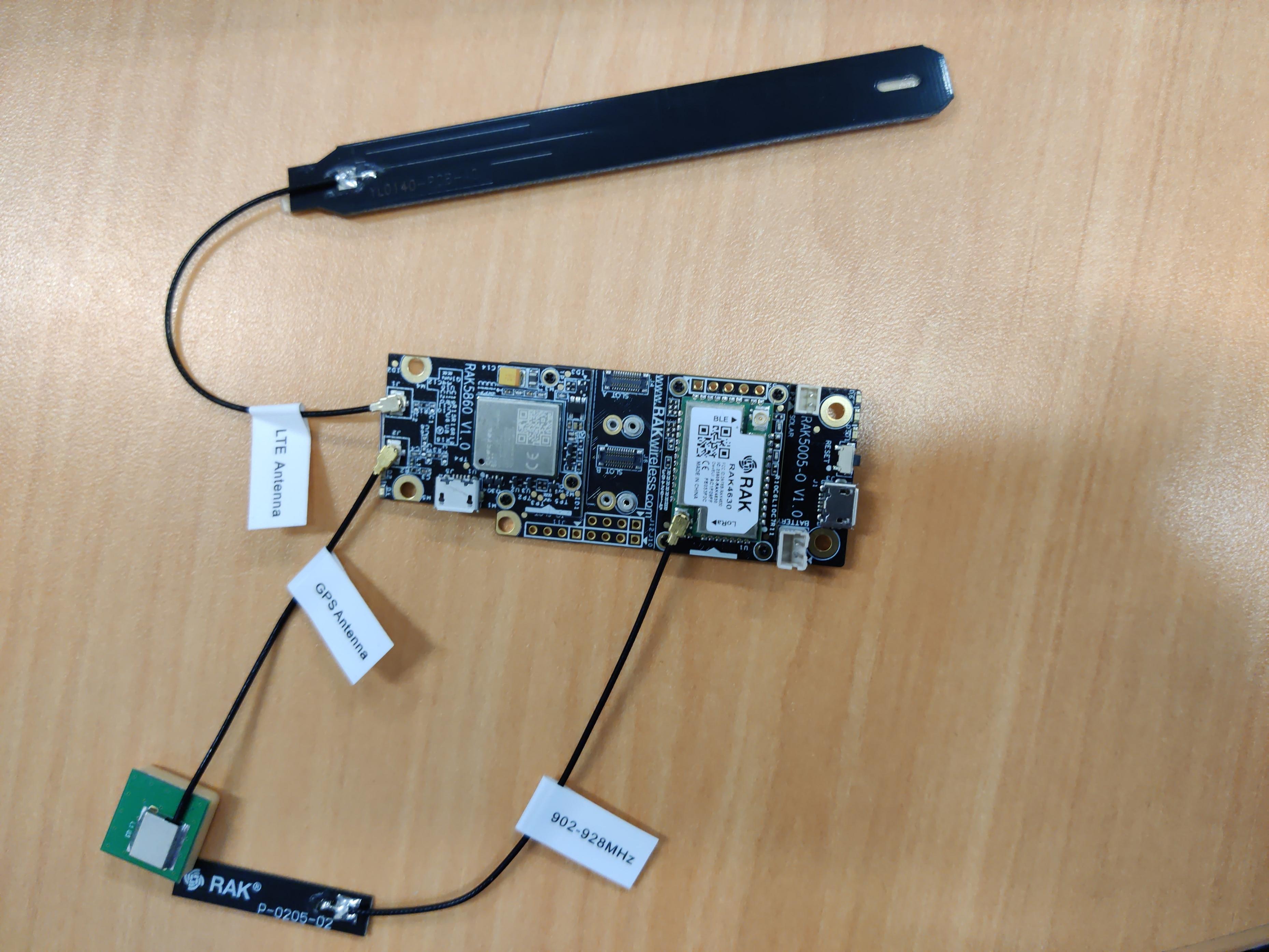

Formerly a Graduate Researcher in Software Defined Radio (SDR) and Autonomous Systems. Outside of FPGAs, I design production-grade software systems — including a 24,700-line AI content pipeline orchestrated by Temporal, and a self-hosted AI infrastructure stack running 12 models across 15 Docker services on a single GPU. I enjoy solving problems where nanoseconds matter — and problems where 55 distributed activities need to compose reliably.

⚡ Low-Latency Specialization

📋 Quick Info

- Name: Ajaya Dahal

- Location: 📍 Austin, TX

- Email: ajayadahal1000@gmail.com

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)